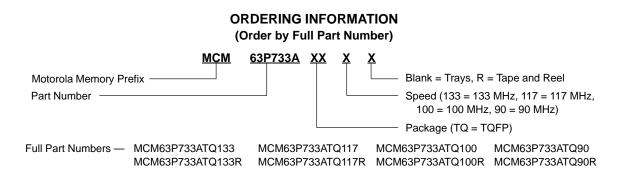

# Advance Information 128K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM

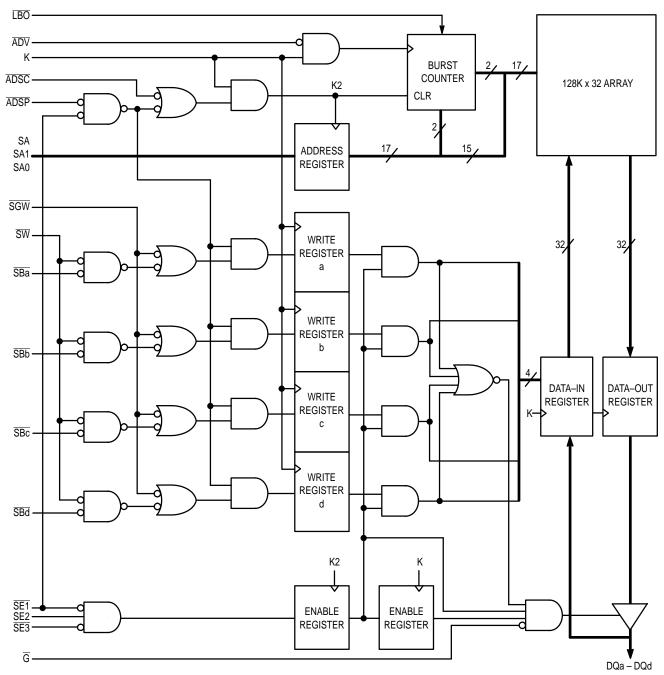

The MCM63P733A is a 4M–bit synchronous fast static RAM designed to provide a burstable, high performance, secondary cache for the PowerPC<sup>™</sup> and other high performance microprocessors. It is organized as 128K words of 32 bits each, fabricated with high performance silicon gate CMOS technology. This device integrates input registers, an output register, a 2–bit address counter, and high speed SRAM onto a single monolithic circuit for reduced parts count in cache data RAM applications. Synchronous design allows precise cycle control with the use of an external clock (K). CMOS circuitry reduces the overall power consumption of the integrated functions for greater reliability.

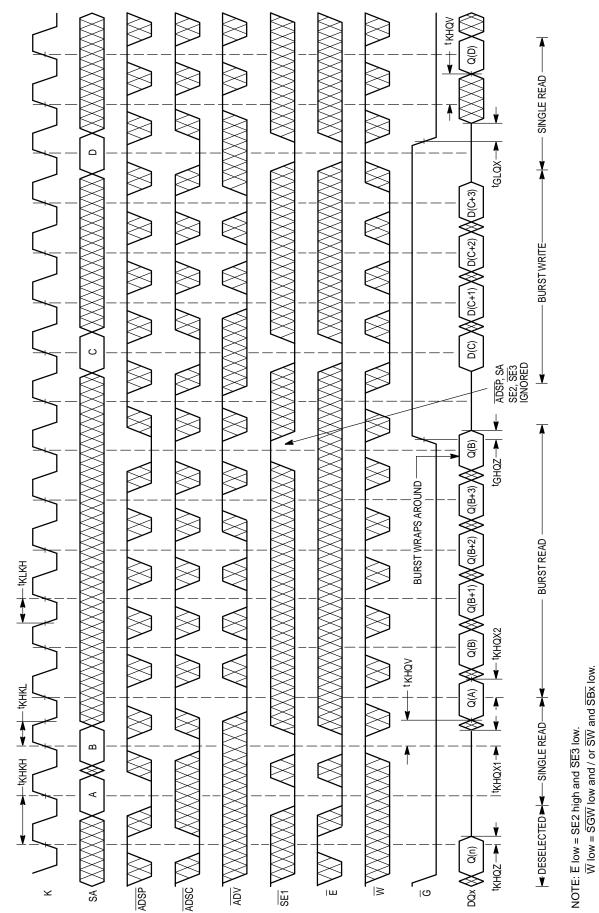

Addresses (SA), data inputs (DQx), and all control signals except output enable ( $\overline{G}$ ) and Linear Burst Order ( $\overline{LBO}$ ) are clock (K) controlled through positive–edge–triggered noninverting registers.

Bursts can be initiated with either ADSP or ADSC input pins. Subsequent burst addresses can be generated internally by the MCM63P733A (burst sequence operates in linear or interleaved mode dependent upon state of LBO) and controlled by the burst address advance (ADV) input pin.

Write cycles are internally self-timed and are initiated by the rising edge of the clock (K) input. This feature eliminates complex off-chip write pulse generation and provides increased timing flexibility for incoming signals.

Synchronous byte write ( $\overline{SBx}$ ), synchronous global write ( $\overline{SGW}$ ), and synchronous write enable ( $\overline{SW}$ ) are provided to allow writes to either individual bytes or to all bytes. The four bytes are designated as "a", "b", "c", and "d".  $\overline{SBa}$  controls DQa,  $\overline{SBb}$  controls DQb, etc. Individual bytes are written if the selected byte writes  $\overline{SBx}$  are asserted with  $\overline{SW}$ . All bytes are written if either  $\overline{SGW}$  is asserted or if all  $\overline{SBx}$  and  $\overline{SW}$  are asserted.

For read cycles, pipelined SRAMs output data is temporarily stored by an edge–triggered output register and then released to the output buffers at the next rising edge of clock (K).

The MCM63P733A operates from a 3.3 V core power supply and all outputs operate on a 2.5 V or 3.3 V power supply. All inputs and outputs are JEDEC standard JESD8–5 compatible.

- MCM63P733A-133 = 4 ns Access/7.5 ns Cycle (133 MHz) MCM63P733A-117 = 4.2 ns Access/8.5 ns Cycle (117 MHz) MCM63P733A-100 = 4.5 ns Access/10 ns Cycle (100 MHz) MCM63P733A-90 = 5 ns Access/11 ns Cycle (90 MHz)

- 3.3 V + 10%/- 5% Core, Power Supply, 2.5 V or 3.3 V I/O Supply

- ADSP, ADSC, and ADV Burst Control Pins

- Selectable Burst Sequencing Order (Linear/Interleaved)

- Internally Self-Timed Write Cycle

- Byte Write and Global Write Control

- Single-Cycle Deselect

- Sleep Mode (ZZ)

- 100-Pin TQFP Package

### PowerPC is a trademark of IBM Corp.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

REV 1 3/24/98

**MCM63P733A**

FUNCTIONAL BLOCK DIAGRAM

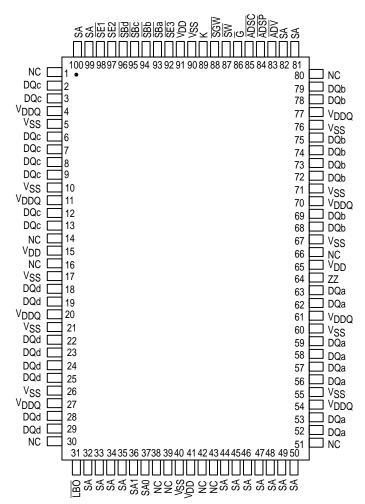

### **PIN ASSIGNMENT**

### **PIN DESCRIPTIONS**

| Pin Locations                                                                                                                                                 | Symbol          | Туре   | Description                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 85                                                                                                                                                            | ADSC            | Input  | Synchronous Address Status Controller: Active low, interrupts any ongoing burst and latches a new external address. Used to initiate a READ, WRITE, or chip deselect.                                                                                                                                                                           |

| 84                                                                                                                                                            | ADSP            | Input  | Synchronous Address Status Processor: Active low, interrupts any ongoing burst and latches a new external address. Used to initiate a new READ, WRITE, or chip deselect (exception — chip deselect does not occur when ADSP is asserted and SE1 is high).                                                                                       |

| 83                                                                                                                                                            | ADV             | Input  | Synchronous Address Advance: Increments address count in accordance with counter type selected (linear/interleaved).                                                                                                                                                                                                                            |

| (a) 51, 52, 53, 56, 57, 58, 59, 62, 63<br>(b) 68, 69, 72, 73, 74, 75, 78, 79, 80<br>(c) 1, 2, 3, 6, 7, 8, 9, 12, 13<br>(d) 18, 19, 22, 23, 24, 25, 28, 29, 30 | DQx             | I/O    | Synchronous Data I/O: "x" refers to the byte being read or written (byte a, b, c, d).                                                                                                                                                                                                                                                           |

| 86                                                                                                                                                            | G               | Input  | Asynchronous Output Enable Input.                                                                                                                                                                                                                                                                                                               |

| 89                                                                                                                                                            | К               | Input  | Clock: This signal registers the address, data in, and all control signals except $\overline{G}$ , $\overline{LBO}$ , and ZZ.                                                                                                                                                                                                                   |

| 31                                                                                                                                                            | LBO             | Input  | Linear Burst Order Input: This pin may be left floating; it will default<br>as interleaved.<br>Low — linear burst counter (68K/PowerPC).<br>High — interleaved burst counter (486/i960/Pentium).                                                                                                                                                |

| 32, 33, 34, 35, 44, 45, 46,<br>47, 48, 49, 50, 81, 82, 99, 100                                                                                                | SA              | Input  | Synchronous Address Inputs: These inputs are registered and must meet setup and hold times.                                                                                                                                                                                                                                                     |

| 36, 37                                                                                                                                                        | SA1, SA0        | Input  | Synchronous Address Inputs: These pins must be wired to the two LSBs of the address bus for proper burst operation. These inputs are registered and must meet setup and hold times.                                                                                                                                                             |

| 93, 94, 95, 96<br>(a) (b) (c) (d)                                                                                                                             | SBx             | Input  | Synchronous Byte Write Inputs: "x" refers to the byte being written (byte a, b, c, d). $\overline{SGW}$ overrides $\overline{SBx}$ .                                                                                                                                                                                                            |

| 98                                                                                                                                                            | SE1             | Input  | Synchronous Chip Enable: Active low to enable chip.<br>Negated high — blocks ADSP or deselects chip when ADSC is<br>asserted.                                                                                                                                                                                                                   |

| 97                                                                                                                                                            | SE2             | Input  | Synchronous Chip Enable: Active high for depth expansion.                                                                                                                                                                                                                                                                                       |

| 92                                                                                                                                                            | SE3             | Input  | Synchronous Chip Enable: Active low for depth expansion.                                                                                                                                                                                                                                                                                        |

| 88                                                                                                                                                            | SGW             | Input  | Synchronous Global Write: This signal writes all bytes regardless of the status of the $\overline{SBx}$ and $\overline{SW}$ signals. If only byte write signals $\overline{SBx}$ are being used, tie this pin high.                                                                                                                             |

| 87                                                                                                                                                            | SW              | Input  | Synchronous Write: This signal writes only those bytes that have been selected using the byte write $\overline{SBx}$ pins. If only byte write signals $\overline{SBx}$ are being used, tie this pin low.                                                                                                                                        |

| 64                                                                                                                                                            | ZZ              | Input  | Sleep Mode: This active high asynchronous signal places the RAM<br>into the lowest power mode. The ZZ pin disables the RAMs internal<br>clock when placed in this mode. When ZZ is negated, the RAM<br>remains in low power mode until it is commanded to READ or<br>WRITE. Data integrity is maintained upon returning to normal<br>operation. |

| 15, 41, 65, 91                                                                                                                                                | V <sub>DD</sub> | Supply | Core Power Supply.                                                                                                                                                                                                                                                                                                                              |

| 4, 11, 20, 27, 54, 61, 70, 77                                                                                                                                 | VDDQ            | Supply | I/O Power Supply.                                                                                                                                                                                                                                                                                                                               |

| 5, 10, 17, 21, 26, 40,<br>55, 60, 67, 71, 76, 90                                                                                                              | VSS             | Supply | Ground.                                                                                                                                                                                                                                                                                                                                         |

| 14, 16, 38, 39, 42, 43, 66                                                                                                                                    | NC              |        | No Connection: There is no connection to the chip.                                                                                                                                                                                                                                                                                              |

### TRUTH TABLE (See Notes 1 through 5)

| Next Cycle     | Address<br>Used | SE1 | SE2 | SE3 | ADSP | ADSC | ADV | <u>G</u> 3 | DQx    | Write <sup>2, 4</sup> |

|----------------|-----------------|-----|-----|-----|------|------|-----|------------|--------|-----------------------|

| Deselect       | None            | 1   | Х   | Х   | Х    | 0    | Х   | Х          | High–Z | Х                     |

| Deselect       | None            | 0   | Х   | 1   | 0    | Х    | Х   | Х          | High–Z | Х                     |

| Deselect       | None            | 0   | 0   | Х   | 0    | Х    | Х   | Х          | High–Z | Х                     |

| Deselect       | None            | Х   | Х   | 1   | 1    | 0    | Х   | Х          | High–Z | Х                     |

| Deselect       | None            | Х   | 0   | Х   | 1    | 0    | Х   | Х          | High–Z | Х                     |

| Begin Read     | External        | 0   | 1   | 0   | 0    | Х    | Х   | Х          | High–Z | Х                     |

| Begin Read     | External        | 0   | 1   | 0   | 1    | 0    | Х   | Х          | High–Z | READ                  |

| Continue Read  | Next            | Х   | Х   | Х   | 1    | 1    | 0   | 1          | High–Z | READ                  |

| Continue Read  | Next            | Х   | Х   | Х   | 1    | 1    | 0   | 0          | DQ     | READ                  |

| Continue Read  | Next            | 1   | Х   | Х   | Х    | 1    | 0   | 1          | High–Z | READ                  |

| Continue Read  | Next            | 1   | Х   | Х   | Х    | 1    | 0   | 0          | DQ     | READ                  |

| Suspend Read   | Current         | Х   | Х   | Х   | 1    | 1    | 1   | 1          | High–Z | READ                  |

| Suspend Read   | Current         | Х   | Х   | Х   | 1    | 1    | 1   | 0          | DQ     | READ                  |

| Suspend Read   | Current         | 1   | Х   | Х   | Х    | 1    | 1   | 1          | High–Z | READ                  |

| Suspend Read   | Current         | 1   | Х   | Х   | Х    | 1    | 1   | 0          | DQ     | READ                  |

| Begin Write    | External        | 0   | 1   | 0   | 1    | 0    | Х   | Х          | High–Z | WRITE                 |

| Continue Write | Next            | Х   | Х   | Х   | 1    | 1    | 0   | Х          | High–Z | WRITE                 |

| Continue Write | Next            | 1   | Х   | Х   | х    | 1    | 0   | Х          | High–Z | WRITE                 |

| Suspend Write  | Current         | Х   | Х   | Х   | 1    | 1    | 1   | Х          | High–Z | WRITE                 |

| Suspend Write  | Current         | 1   | Х   | Х   | Х    | 1    | 1   | Х          | High–Z | WRITE                 |

NOTES:

1. X = Don't Care. 1 = logic high. 0 = logic low.

2. Write is defined as either 1) any SBx and SW low, or 2) SGW is low.

3.  $\overline{G}$  is an asynchronous signal and is not sampled by the clock K.  $\overline{G}$  drives the bus immediately (t<sub>GLQX</sub>) following  $\overline{G}$  going low.

4. On write cycles that follow read cycles,  $\overline{G}$  must be negated prior to the start of the write cycle to ensure proper write data setup times.  $\overline{G}$  must also remain negated at the completion of the write cycle to ensure proper write data hold times.

### ASYNCHRONOUS TRUTH TABLE

| Operation  | ZZ | G | I/O Status     |

|------------|----|---|----------------|

| Read       | L  | L | Data Out (DQx) |

| Read       | L  | Н | High–Z         |

| Write      | L  | Х | High–Z         |

| Deselected | L  | Х | High–Z         |

| Selected   | Н  | Х | High–Z         |

### LINEAR BURST ADDRESS TABLE ( $\overline{LBO} = V_{SS}$ )

| 1st Address (External) | 2nd Address (Internal) | 3rd Address (Internal) | 4th Address (Internal) |

|------------------------|------------------------|------------------------|------------------------|

| X X00                  | X X01                  | X X10                  | X X11                  |

| X X01                  | X X10                  | X X11                  | X X00                  |

| X X10                  | X X11                  | X X00                  | X X01                  |

| X X11                  | X X00                  | X X01                  | X X10                  |

### INTERLEAVED BURST ADDRESS TABLE ( $\overline{LBO} = V_{DD}$ )

| 1st Address (External) | 2nd Address (Internal) | 3rd Address (Internal) | 4th Address (Internal) |

|------------------------|------------------------|------------------------|------------------------|

| X X00                  | X X01                  | X X10                  | X X11                  |

| X X01                  | X X00                  | X X11                  | X X10                  |

| X X10                  | X X11                  | X X00                  | X X01                  |

| X X11                  | X X10                  | X X01                  | X X00                  |

### WRITE TRUTH TABLE

| Сусіе Туре      | SGW | SW | SBa | SBb | SBc | SBd |

|-----------------|-----|----|-----|-----|-----|-----|

| Read            | Н   | н  | Х   | Х   | Х   | Х   |

| Read            | Н   | L  | н   | Н   | н   | н   |

| Write Byte a    | Н   | L  | L   | Н   | Н   | н   |

| Write Byte b    | Н   | L  | Н   | L   | Н   | н   |

| Write Byte c    | Н   | L  | Н   | Н   | L   | н   |

| Write Byte d    | Н   | L  | н   | Н   | н   | L   |

| Write All Bytes | Н   | L  | L   | L   | L   | L   |

| Write All Bytes | L   | Х  | Х   | Х   | Х   | Х   |

### ABSOLUTE MAXIMUM RATINGS (See Note 1)

| Rating                                                                       | Symbol                             | Value                          | Unit | Notes |

|------------------------------------------------------------------------------|------------------------------------|--------------------------------|------|-------|

| Power Supply Voltage                                                         | V <sub>DD</sub>                    | – 0.5 to + 4.6                 | V    |       |

| I/O Supply Voltage                                                           | V <sub>DDQ</sub>                   | $V_{SS}$ – 0.5 to $V_{DD}$     | V    | 2     |

| Input Voltage Relative to $V_{\mbox{SS}}$ for Any Pin Except $V_{\mbox{DD}}$ | V <sub>in</sub> , V <sub>out</sub> | – 0.5 to V <sub>DD</sub> + 0.5 | V    | 2     |

| Input Voltage (Three–State I/O)                                              | VIT                                | -0.5 to V <sub>DDQ</sub> + 0.5 | V    | 2     |

| Output Current (per I/O)                                                     | l <sub>out</sub>                   | ± 20                           | mA   |       |

| Package Power Dissipation                                                    | PD                                 | 1.2                            | W    | 3     |

| Temperature Under Bias                                                       | T <sub>bias</sub>                  | – 10 to + 85                   | °C   |       |

| Storage Temperature                                                          | T <sub>stg</sub>                   | – 55 to + 125                  | °C   |       |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high–impedance circuit.

NOTES:

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPER-ATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

2. This is a steady-state DC parameter that is in effect after the power supply has achieved its nominal operating level. Power sequencing is not necessary.

3. Power dissipation capability is dependent upon package characteristics and use environment. See Package Thermal Characteristics.

### PACKAGE THERMAL CHARACTERISTICS

| Rating                          |                                        | Symbol           | Мах      | Unit | Notes |

|---------------------------------|----------------------------------------|------------------|----------|------|-------|

| Junction to Ambient (@ 200 lfm) | Single–Layer Board<br>Four–Layer Board | R <sub>θJA</sub> | 40<br>25 | °C/W | 1, 2  |

| Junction to Board (Bottom)      |                                        | R <sub>θJB</sub> | 17       | °C/W | 3     |

| Junction to Case (Top)          |                                        | R <sub>θJC</sub> | 9        | °C/W | 4     |

NOTES:

1. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, board population, and board thermal resistance.

2. Per SEMI G38-87.

3. Indicates the average thermal resistance between the die and the printed circuit board.

4. Indicates the average thermal resistance between the die and the case top surface via the cold plate method (MIL SPEC-883 Method 1012.1).

### DC OPERATING CONDITIONS AND CHARACTERISTICS

(V<sub>DD</sub> = 3.3 V + 10%, -5%, T<sub>A</sub> = 0 to 70°C, Unless Otherwise Noted)

## **RECOMMENDED OPERATING CONDITIONS: 2.5 V I/O Supply** (Voltages Referenced to $V_{SS} = 0 V$ )

| Parameter                                      | Symbol           | Min   | Тур | Max                    | Unit |

|------------------------------------------------|------------------|-------|-----|------------------------|------|

| Supply Voltage                                 | V <sub>DD</sub>  | 3.135 | 3.3 | 3.6                    | V    |

| I/O Supply Voltage                             | V <sub>DDQ</sub> | 2.375 | 2.5 | 2.9                    | V    |

| Input Low Voltage                              | VIL              | - 0.3 | _   | 0.7                    | V    |

| Input High Voltage                             | VIH              | 1.7   | _   | V <sub>DD</sub> + 0.3  | V    |

| Input High Voltage (I/O Pins)                  | V <sub>IH2</sub> | 1.7   | _   | V <sub>DDQ</sub> + 0.3 | V    |

| Output Low Voltage (I <sub>OL</sub> = 2 mA)    | V <sub>OL</sub>  | _     | _   | 0.7                    | V    |

| Output High Voltage (I <sub>OH</sub> = - 2 mA) | VOH              | 1.7   | _   | —                      | V    |

### RECOMMENDED OPERATING CONDITIONS: 3.3 V I/O Supply (Voltages Referenced to V<sub>SS</sub> = 0 V)

| Parameter                                      | Symbol           | Min   | Тур | Max                    | Unit |

|------------------------------------------------|------------------|-------|-----|------------------------|------|

| Supply Voltage                                 | V <sub>DD</sub>  | 3.135 | 3.3 | 3.6                    | V    |

| I/O Supply Voltage                             | V <sub>DDQ</sub> | 3.135 | 3.3 | V <sub>DD</sub>        | V    |

| Input Low Voltage                              | VIL              | - 0.5 | _   | 0.8                    | V    |

| Input High Voltage                             | VIH              | 2     | _   | V <sub>DD</sub> + 0.5  | V    |

| Input High Voltage (I/O Pins)                  | VIH2             | 2     | _   | V <sub>DDQ</sub> + 0.5 | V    |

| Output Low Voltage (I <sub>OL</sub> = 8 mA)    | VOL              | —     | _   | 0.4                    | V    |

| Output High Voltage (I <sub>OH</sub> = - 4 mA) | VOH              | 2.4   | _   | —                      | V    |

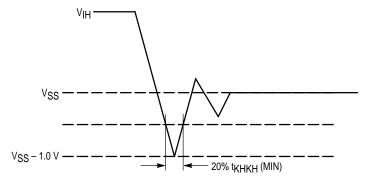

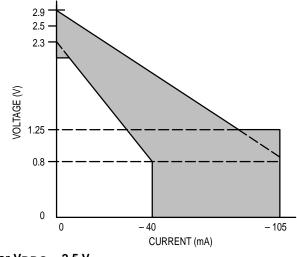

Figure 1. Undershoot Voltage

### SUPPLY CURRENTS

| Parameter                                                                                                                                                                           | Symbol              | Min | Тур | Max | Unit | Notes            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|------------------|

| Input Leakage Current (0 V $\leq$ V <sub>in</sub> $\leq$ V <sub>DD</sub> )                                                                                                          | I <sub>lkg(I)</sub> | —   | -   | ± 1 | μΑ   | 1, 2             |

| Output Leakage Current (0 V $\leq$ V <sub>in</sub> $\leq$ V <sub>DDQ</sub> )                                                                                                        | I <sub>lkg(O)</sub> | —   | -   | ± 1 | μA   |                  |

| AC Supply Current (Device Selected,<br>All Outputs Open, Freq = Max)MCM63P733A-13<br>MCM63P733A-11<br>MCM63P733A-10<br>MCM63P733A-30Includes VDD OnlyMCM63P733A-30<br>MCM63P733A-30 | 7                   | _   | _   | TBD | mA   | 3, 4, 5          |

| CMOS Standby Supply Current (Device Deselected, Freq = $V_{DD}$ = Max, All Inputs Static at CMOS Levels)                                                                            | ), I <sub>SB2</sub> | -   | -   | TBD | mA   | 6, 8             |

| Sleep Mode Supply Current (Sleep Mode, Freq = Max, $V_{DD}$ = Max, All Other Inputs Static at CMOS Levels, $ZZ \ge V_{DD} - 0.2 V$ )                                                | IZZ                 | _   | -   | 2   | mA   | 2, 7, 8          |

| TTL Standby Supply Current (Device Deselected, Freq = 0, $V_{DD}$ = Max, All Inputs Static at TTL Levels)                                                                           | I <sub>SB3</sub>    | -   | -   | TBD | mA   | 6, 9             |

| Clock Running (Device Deselected,<br>Freq = Max, VDD = Max, All InputsMCM63P733A-13<br>MCM63P733A-11Toggling at CMOS Levels)MCM63P733A-10<br>MCM63P733A-60                          | 7                   | _   | _   | TBD | mA   | 3, 4,<br>5, 6, 8 |

| Static Clock Running (Device Deselected, MCM63P733A-13Freq = Max, VDD = Max, All InputsMCM63P733A-13Static at TTL Levels)MCM63P733A-10MCM63P733A-30MCM63P733A-30                    | 7                   | _   | _   | TBD | mA   | 6, 9             |

NOTES:

1.  $\overline{\text{LBO}}$  pin has an internal pullup and will exhibit leakage currents of  $\pm$  5  $\mu\text{A}.$

2. ZZ pin has an internal pulldown and will exhibit leakage currents of  $\pm\,5\,\mu\text{A}.$

3. Reference AC Operating Conditions and Characteristics for input and timing.

4. All addresses transition simultaneously low (LSB) then high (MSB).

5. Data states are all zero.

6. Device is deselected as defined by the Truth Table.

7. Device in Sleep Mode as defined by the Asynchronous Truth Table.

8. CMOS levels for I/O's are  $V_{IT} \le V_{SS} + 0.2$  V or  $\ge V_{DDQ} - 0.2$  V. CMOS levels for other inputs are  $V_{in} \le V_{SS} + 0.2$  V or  $\ge V_{DD} - 0.2$  V. 9. TTL levels for I/O's are  $V_{IT} \le V_{IL}$  or  $\ge V_{IH2}$ . TTL levels for other inputs are  $V_{in} \le V_{IL}$  or  $\ge V_{IH}$ .

### CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, T<sub>A</sub> = 0 to 70°C, Periodically Sampled Rather Than 100% Tested)

| Parameter                | Symbol           | Min | Тур | Max | Unit |

|--------------------------|------------------|-----|-----|-----|------|

| Input Capacitance        | C <sub>in</sub>  | —   | 4   | 5   | pF   |

| Input/Output Capacitance | C <sub>I/O</sub> | —   | 7   | 8   | pF   |

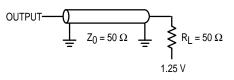

### AC OPERATING CONDITIONS AND CHARACTERISTICS

(V<sub>DD</sub> = 3.3 V + 10%, -5%, T<sub>A</sub> = 0 to 70°C, Unless Otherwise Noted)

| Input Timing Measurement Reference Level | 1.25 V |

|------------------------------------------|--------|

| Input Pulse Levels 0 to                  | 2.5 V  |

| Input Rise/Fall Time 1.0 V/ns (20 to     | 80%)   |

|                                                                            |                                                                                                         | 63P733<br>133            |                          | 63P733<br>117            |                          | 63P733<br>100            | 3A–100<br>MHz            |                          | 3A–90<br>MHz             |      |       |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------|-------|

| Parameter                                                                  | Symbol                                                                                                  | Min                      | Max                      | Min                      | Max                      | Min                      | Max                      | Min                      | Max                      | Unit | Notes |

| Cycle Time                                                                 | <sup>t</sup> КНКН                                                                                       | 7.5                      | _                        | 8.5                      | —                        | 10                       | —                        | 11                       | —                        | ns   |       |

| Clock High Pulse Width                                                     | <sup>t</sup> KHKL                                                                                       | 3                        | —                        | 3.4                      | —                        | 4                        | —                        | 4.4                      | —                        | ns   |       |

| Clock Low Pulse Width                                                      | <sup>t</sup> KLKH                                                                                       | 3                        | _                        | 3.4                      | —                        | 4                        | —                        | 4.4                      | —                        | ns   |       |

| Clock Access Time                                                          | <sup>t</sup> KHQV                                                                                       | —                        | 4                        | _                        | 4.2                      | —                        | 4.5                      | —                        | 5                        | ns   |       |

| Output Enable to Output<br>Valid                                           | <sup>t</sup> GLQV                                                                                       | —                        | 3.8                      | —                        | 3.8                      | —                        | 4.5                      | —                        | 5                        | ns   |       |

| Clock High to Output<br>Active                                             | <sup>t</sup> KHQX1                                                                                      | 0                        | -                        | 0                        | —                        | 0                        | —                        | 0                        | -                        | ns   | 5, 6  |

| Clock High to Output<br>Change                                             | <sup>t</sup> KHQX2                                                                                      | 1.5                      | —                        | 1.5                      | —                        | 1.5                      | -                        | 1.5                      | -                        | ns   | 6     |

| Output Enable to Output<br>Active                                          | <sup>t</sup> GLQX                                                                                       | 0                        | -                        | 0                        | —                        | 0                        | -                        | 0                        | -                        | ns   | 5, 6  |

| Output Disable to Q<br>High–Z                                              | <sup>t</sup> GHQZ                                                                                       | _                        | 3.8                      | —                        | 3.8                      | —                        | 4.5                      | _                        | 5                        | ns   | 5, 6  |

| Clock High to Q High–Z                                                     | <sup>t</sup> KHQZ                                                                                       | 1.5                      | 7.5                      | 1.5                      | 8.5                      | 1.5                      | 10                       | 1.5                      | 11                       | ns   | 5, 6  |

| Setup Times: Address<br>ADSP, ADSC, ADV<br>Data In<br>Write<br>Chip Enable | <sup>t</sup> ADKH<br><sup>t</sup> ADSKH<br><sup>t</sup> DVKH<br><sup>t</sup> WVKH<br><sup>t</sup> EVKH  | 2                        | _                        | 2                        | _                        | 2                        | _                        | 2                        | _                        | ns   |       |

| Hold Times: Address<br>ADSP, ADSC, ADV<br>Data In<br>Write<br>Chip Enable  | <sup>t</sup> KHAX<br><sup>t</sup> KHADSX<br><sup>t</sup> KHDX<br><sup>t</sup> KHWX<br><sup>t</sup> KHEX | 0.5                      | _                        | 0.5                      | _                        | 0.5                      | _                        | 0.5                      | _                        | ns   |       |

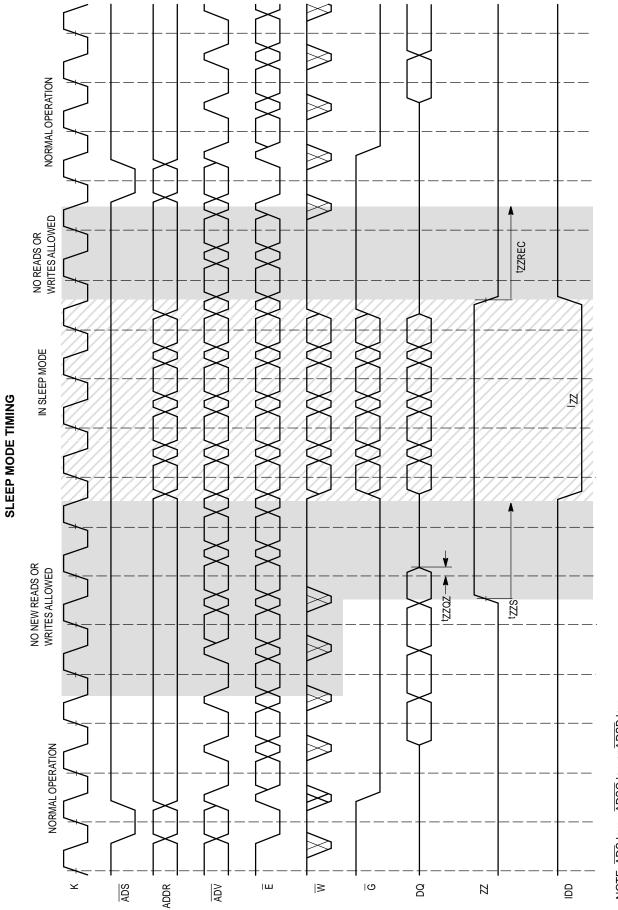

| Sleep Mode Standby                                                         | tzzs                                                                                                    | _                        | 2 x<br><sup>t</sup> KHKH | ns   |       |

| Sleep Mode Recovery                                                        | <sup>t</sup> ZZREC                                                                                      | 2 x<br><sup>t</sup> KHKH | _                        | 2 x<br><sup>t</sup> KHKH | —                        | 2 x<br><sup>t</sup> KHKH | -                        | 2 x<br><sup>t</sup> KHKH | _                        | ns   |       |

| Sleep Mode High to Q<br>High–Z                                             | <sup>t</sup> ZZQZ                                                                                       | _                        | 15                       | —                        | 15                       | —                        | 15                       | —                        | 15                       | ns   |       |

NOTES:

1. Write is defined as either any SBx and SW low or SGW is low. Chip Enable is defined as SE1 low, SE2 high, and SE3 low whenever ADSP or ADSC is asserted.

2. All read and write cycle timings are referenced from K or  $\overline{G}$ .

3.  $\overline{G}$  is a don't care after write cycle begins. To prevent bus contention,  $\overline{G}$  should be negated prior to start of write cycle.

4. In order to reduce test correlation issues and to reduce the effects of application specific input edge rate variations on correlation between data sheet parameters and actual system performance, FSRAM AC parametric specifications are always specified at V<sub>DDQ</sub>/2. In some design exercises, it is desirable to evaluate timing using other reference levels. Since the maximum test input edge rate is known and is given in the AC Test Conditions section of the data sheet as 1 V/ns, one can easily interpolate timing values to other reference levels.

5. This parameter is sampled and not 100% tested.

6. Measured at  $\pm\,200$  mV from steady state.

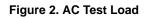

Figure 3. Lumped Capacitive Load and Typical Derating Curve

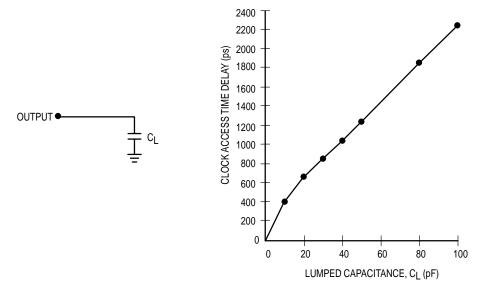

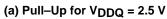

| PULL-UP     |            |            |  |  |  |

|-------------|------------|------------|--|--|--|

| VOLTAGE (V) | l (mA) MIN | l (mA) MAX |  |  |  |

| - 0.5       | - 38       | - 105      |  |  |  |

| 0           | - 38       | - 105      |  |  |  |

| 0.8         | - 38       | - 105      |  |  |  |

| 1.25        | - 30       | - 83       |  |  |  |

| 1.5         | - 27       | - 75       |  |  |  |

| 2.3         | 0          | - 40       |  |  |  |

| 2.7         | 0          | - 15       |  |  |  |

| 2.9         | 0          | 0          |  |  |  |

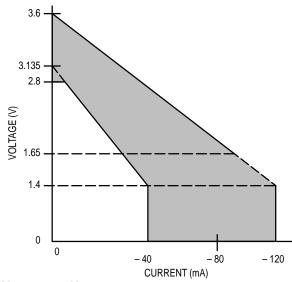

| PULL-UP     |            |            |  |  |  |

|-------------|------------|------------|--|--|--|

| VOLTAGE (V) | l (mA) MIN | l (mA) MAX |  |  |  |

| - 0.5       | - 40       | - 120      |  |  |  |

| 0           | - 40       | - 120      |  |  |  |

| 1.4         | - 40       | - 120      |  |  |  |

| 1.65        | - 37       | - 108      |  |  |  |

| 2.0         | - 28       | - 81       |  |  |  |

| 3.135       | 0          | - 20       |  |  |  |

| 3.6         | 0          | 0          |  |  |  |

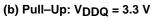

| PULL-DOWN   |            |            |  |  |  |  |

|-------------|------------|------------|--|--|--|--|

| VOLTAGE (V) | l (mA) MIN | I (mA) MAX |  |  |  |  |

| - 0.5       | 0          | 0          |  |  |  |  |

| 0           | 0          | 0          |  |  |  |  |

| 0.4         | 10         | 20         |  |  |  |  |

| 0.8         | 20         | 40         |  |  |  |  |

| 1.25        | 31         | 63         |  |  |  |  |

| 1.6         | 40         | 80         |  |  |  |  |

| 2.8         | 40         | 80         |  |  |  |  |

| 3.2         | 40         | 80         |  |  |  |  |

| 3.4         | 40         | 80         |  |  |  |  |

(c) Pull–Down

Figure 4. Typical Output Buffer Characteristics

READ/WRITE CYCLES

MCM63P733A 12

NOTE:  $\overline{ADS}$  low =  $\overline{ADSC}$  low or  $\overline{ADSP}$  low.  $\overline{ADS}$  high = both  $\overline{ADSC}$ ,  $\overline{ADSP}$  high.  $\overline{E}$  low =  $\overline{SE1}$  low, SE2 high,  $\overline{SE3}$  low. IZZ (max) specifications will not be met if inputs toggle.

### SLEEP MODE

A sleep mode feature, the ZZ pin, has been implemented on the MCM63P733A. It allows the system designer to place the RAM in the lowest possible power condition by asserting ZZ. The sleep mode timing diagram shows the different modes of operation: Normal Operation, No READ/WRITE Allowed, and Sleep Mode. Each mode has its own set of constraints and conditions that are allowed.

Normal Operation: All inputs must meet setup and hold times prior to sleep and t<sub>ZZREC</sub> nanoseconds after recovering from sleep. Clock (K) must also meet cycle, high, and low times during these periods. Two cycles prior to sleep, initiation of either a read or write operation is not allowed.

No READ/WRITE: During the period of time just prior to sleep and during recovery from sleep, the assertion of either ADSC, ADSP, or any write signal is not allowed. If a write operation occurs during these periods, the memory array may be corrupted. Validity of data out from the RAM can not be guaranteed immediately after ZZ is asserted (prior to being in sleep).

Sleep Mode: The RAM automatically deselects itself. The RAM disconnects its internal clock buffer. The external clock

may continue to run without impacting the RAMs sleep current ( $I_{ZZ}$ ). All inputs are allowed to toggle — the RAM will not be selected and perform any reads or writes. However, if inputs toggle, the  $I_{ZZ}$  (max) specification will not be met.

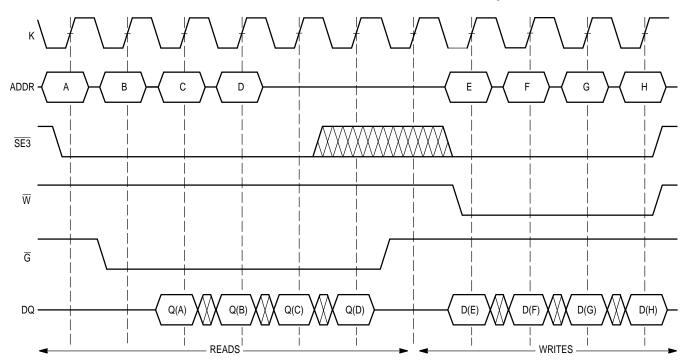

### NON-BURST SYNCHRONOUS OPERATION

Although this BurstRAM has been designed for PowerPC — and other high end MPU–based systems, these SRAMs can be used in other high speed L2 cache or memory applications that do not require the burst address feature. Most L2 caches designed with a synchronous interface can make use of the MCM63P733A. The burst counter feature of the BurstRAM can be disabled, and the SRAM can be configured to act upon a continuous stream of addresses. See Figure 4.

### CONTROL PIN TIE VALUES EXAMPLE (H $\ge$ V<sub>IH</sub>, L $\le$ V<sub>IL</sub>)

| Non-Burst                         | ADSP | ADSC | ADV | SE1 | SE2 | LBO |

|-----------------------------------|------|------|-----|-----|-----|-----|

| Sync Non–Burst,<br>Pipelined SRAM | Н    | L    | Н   | L   | Н   | х   |

NOTE: Although X is specified in the table as a don't care, the pin must be tied either high or low.

Figure 5. Example Configuration as Non–Burst Synchronous SRAM

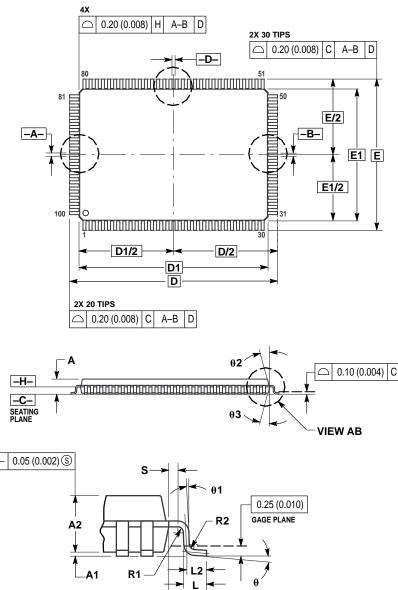

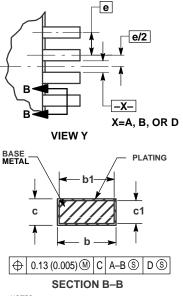

### **TQ PACKAGE** 100-PIN TQFP CASE 983A-01

VIEW AB

L1

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER. DATUM PLANE -H- IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD 2. 3.

- LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE. 4. DATUMS -A-, -B- AND -D- TO BE DETERMINED AT DATUM PLANE -H-. 5. DIMENSIONS D AND E TO BE DETERMINED AT SEATING PLANE -C-. 6. DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 (0.010) PER SIDE. DIMENSIONS D1 AND B1 DO INCL UDE MOLD MISMATCH AND APE B1 DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- DETERMINED AT DATUM PLANE ----. DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE b DIMENSION TO EXCEED 0.45 7. (0.018).

|     | MILLIN   | IETERS   | INC       | HES   |  |

|-----|----------|----------|-----------|-------|--|

| DIM | MIN      | MAX      | MIN       | MAX   |  |

| Α   |          | 1.60     |           | 0.063 |  |

| A1  | 0.05     | 0.15     | 0.002     | 0.006 |  |

| A2  | 1.35     | 1.45     | 0.053     | 0.057 |  |

| b   | 0.22     | 0.38     | 0.009     | 0.015 |  |

| b1  | 0.22     | 0.33     | 0.009     | 0.013 |  |

| С   | 0.09     | 0.20     | 0.004     | 0.008 |  |

| c1  | 0.09     | 0.16     | 0.004     | 0.006 |  |

| D   | 22.00    | BSC      | 0.866 BSC |       |  |

| D1  | 20.00    | BSC      | 0.787 BSC |       |  |

| E   | 16.00    | BSC      | 0.630 BSC |       |  |

| E1  | 14.00    | BSC      | 0.551 BSC |       |  |

| е   | 0.65 BSC |          | 0.026 BSC |       |  |

| L   | 0.45     | 0.75     | 0.018     | 0.030 |  |

| L1  | 1.00 REF |          | 0.039 REF |       |  |

| L2  | 0.50     | 0.50 REF |           | REF   |  |

| S   | 0.20     |          | 0.008     |       |  |

| R1  | 0.08     |          | 0.003     |       |  |

| R2  | 0.08     | 0.20     | 0.003     | 0.008 |  |

| θ   | 0 °      | 7 °      | 0 °       | 7°    |  |

| θ1  | 0 °      |          | 0 °       |       |  |

| θ2  | 11 °     | 13 °     | 11 °      | 13°   |  |

| θ3  | 11 °     | 13 °     | 11 °      | 13°   |  |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **(A)** are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employee.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado, 80217. 1-303-675-2140 or 1-800-441-2447

Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE 1-602-244-6609 Motorola Fax Back System - US & Canada ONLY 1-800-774-1848 - http://sps.motorola.com/mfax/

$\Diamond$

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

JAPAN: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 141, 4-32-1 Nishi-Gotanda, Shagawa-ku, Tokyo, Japan. 03-5487-8488

TOUCHTONE 1-602-244-6609

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

US & Canada ONLY 1-800-774-1848

51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

CUSTOMER FOCUS CENTER: 1-800-521-6274

MCM63P733A/D